# V93000 HSM HSM6800

### **Product Overview**

Fastest memory at-speed final test solution of ultra high-speed GDDR5 and XDR, scalable to 8Gbps with superior throughput, yield and lowest test cost.

### **Industry Challenges**

High-end workstation, desktop and laptop PCs, computer servers, performance graphics cards, dynamic game consoles, high-end video/HDTV, computer networking and a variety of consumer electronics all depend on performance-oriented Dynamic RAM (DRAM) memory types — DDR3, GDDR5 and XDR — to deliver the latest performance and functionality over a range of selling prices.

The technological accelerating rate of advancement of these market leading electronics drives an increasingly complex set of cost, performance, power and bandwidth requirements. As a fundamental component, Dynamic RAM memory technologies must continuously evolve to match application demands by providing increased data transfer rates (doubling every three to four years) and lower costs per bit.

Increasing memory data transfer rates have forced constant production process geometry shrinks, which cause new failure mechanisms that require thorough at-speed test of the memory I/O and the memory core.

# **ADVANTEST.**

Further, in order to enable data rates in the multigigabit per second range, memory devices have been adopting advanced architectural features from SOC devices, such as forwarded clock architectures and extensive device trainings. These I/O-features raise test requirements that are well known in the high-speed SOC test arena, but are new to conventional memory test systems. Requirements typical for memory test, such as massive multi-site implementations, remain present for high-speed memory devices.

The combination of higher test speeds, growing feature-set requirements and the persistent pressure on lowering test costs results in significant challenges for memory ATE. This traditionally has forced DRAM manufacturers to purchase a new test system for every new generation of memory technology, i.e. every 3-4 years.

Memory manufacturers seek an ATE solution that delivers the performance, functionality and economical requirements of testing high-speed memories - offering best lifetime value and investment protection beyond a single memory device generation.

#### **Product Summary**

Fastest memory at-speed final test solution of ultra high-speed GDDR5 and XDR, scalable to 8Gbps with superior throughput, yield and lowest test cost

The V93000 HSM6800 is the fastest memory solution available today, providing scalable performance to 8.0Gbps and superior throughput and yield for low-cost volume production test of ultra high-speed memory devices, including GDDR5 and XDR.

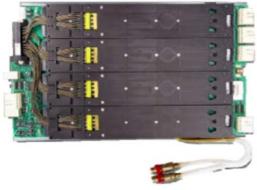

HSM6800 Memory Test Card

#### At-speed final test, scalable to 8Gbps

The HSM6800, targeted for volume production test of ultra high-speed memories, offers native 6.8Gbps at-speed I/O and at-speed memory core access testing up to 64-sites GDDR5 in parallel as well as superior accuracy for best device quality and manufacturing yields.

With its unique twin strobe double clocking feature, the maximum test speed can be scaled to an industry leading 8.0Gbps per pin, addressing the future speeds of all available ultra high-speed memory technologies.

# Superior throughput and yield for lowest cost of test

The unmatched native speed headroom of the HSM6800, with its unique 8Gbps twin strobe double clocking feature, provides true 64-sites parallel test capability over the full speed range without the typical throughput penalties of traditional double clocking or pin-muxing implementations, attempting to increase the native ATE speed limits. The resulting benefit is an industry leading throughput and yield for up to 2x good devices per hour and lowest cost of test.

#### Integrated test-cell maximizes productivity

HSM Manufacturing Test Cell

The V93000 HSM Series comes with an integrated volume manufacturing test-cell, which ensures reliable operation and high uptime as well as efficient one-person operation, comprising tester-to-handler docking, test fixture exchange and test fixture buffer storage within the test-cell for maximized productivity.

- Optimized tester-to-handler docking repeatability

- Flexible floor-plan layout options with small footprint

- Lowest handler index time and cycle time overhead for highest throughput efficiency

- Best temperature accuracy of +/- 1.5°C or better for best production yields

# Characterization up to 12.8Gbps with best engineering tool-set

Proven in R&D & validation labs worldwide, the V93000 HSM Series provides the industry's most advanced high-speed memory test capabilities in a cost-effective, small footprint tester, making it a perfect fit for engineering, design verification & characterization.

Due to the scalability of the V93000 HSM platform, the new generation V93000 HSM memory test cards, HSM6800, HSM4000 and HSM3G, are plug-and-play extensions and can be easily combined with already available memory test cards, such as HSM3600 and HSM HX.

The ability to upgrade existing engineering test systems with latest generation high-speed technology provides flexible access to higher performance and enhanced high-speed test functionality at lowest capital spending.

- Best in industry high-speed performance scalable up to 12.8Gbps with the market proven HSM HX

- Easy to expand capabilities with new generation memory test cards retaining full compatibility

- Compact Test Head, fully compatible to HVM: same hardware, same software, same DUT boards, same ability to use future platform enhancements

- Easy test program transfer and correlation from engineering to production

- Unique Flexibility, addressing DDR3/4, GDDR5 and XDR within one system

Best engineering tool-set: Jitter Injection & Measurement, Pattern controlled DC test, Bitmap, Timing Diagram, Real-time Source-Synchronous, Signal Equalization (and more)

# **Features and Benefits**

| FEATURE | BENEFIT |  |

|---------|---------|--|

|         |         |  |

| 64-sites GDDR5 and XDR at single pass  Native data rate up to 6.8Gbps                     | Avoids "double clocking" or "pin muxing" - provides up to 100% throughput advantage for                                   |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul><li>Native data rate up to 6.8Gbps</li><li>Gbps twin strobe double clocking</li></ul> | test speeds beyond 4.0Gbps as well as best test coverage and yield for best-in-class cost of test                         |  |  |

| <ul><li>Memory ATE per-pin</li><li>Per pin APG</li><li>Per pin pattern memory</li></ul>   | Fully parallel pattern execution, DC tests and eyewidth measurements for best multi-site efficiency.                      |  |  |

| Per pin PMU                                                                               | Up to 20% throughput advantage resulting in lowest cost-of-test                                                           |  |  |

| Simultaneous Bi-directional (SBD)                                                         | At-speed test of I/O pins on a single transmission line without data bus collisions.                                      |  |  |

|                                                                                           | Full at-speed test coverage, shortest test-times (no padding), lowest cost-of test.                                       |  |  |

| Complete feature-set:                                                                     | Ability to test all high-speed failure mechanisms and to ensure high-speed signal integrity                               |  |  |

| <ul> <li>Jitter Injection &amp; Measurement Embedded</li> <li>Parallel Search</li> </ul>  | Highest test-coverage and yield.                                                                                          |  |  |

| <ul> <li>Real-time Strobe Adaptation / Source-<br/>Synchronous</li> </ul>                 |                                                                                                                           |  |  |

| Programmable Signal Equalization                                                          |                                                                                                                           |  |  |

| Per-pin timing                                                                            | Recovery of timing margins for highest yields.                                                                            |  |  |

| Lowest Timing Jitter and lowest skew                                                      | Repeatable, reliable and accurate timing test for highest yields                                                          |  |  |

| Repeatable, reliable and accurate timing test for highest yields                          | Flexibility to address all high-speed memory technologies.                                                                |  |  |

|                                                                                           | Investment protection                                                                                                     |  |  |

| Programmable at-speed APG per-pin  CRC Data Generation                                    | Enables most complex memory test patterns for any fault algorithm to ensure required test quality and fast yield learning |  |  |

| ABI / DBI Support                                                                         | Ready to test advanced I/O capabilities of current and next generation memory architectures                               |  |  |

|                                                                                           |                                                                                                                           |  |  |

# **Key Specifications**

| SPECIFICATION | VALUE |  |  |

|---------------|-------|--|--|

|               |       |  |  |

| Maximum Test Speed:  | 8.0Gbps (6.8Gbps native)                                                                                                                                                                                                                                                  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Example parallelism: | 64-sites GDDR5 256-sites DDR3                                                                                                                                                                                                                                             |  |

| Special Functions:   | <ul> <li>Simultaneous Bi-directional (SBD)</li> <li>Real-Time Strobe Adaptation</li> <li>Embedded Search Support</li> <li>Programmable Signal Equalization</li> <li>Jitter Injection &amp; Measurement</li> <li>CRC Data Generation</li> <li>ABI / DBI Support</li> </ul> |  |

## V93000 HSM System Components / Options

- System Infrastructure: V93000 Infrastructure

- Test-Head Options:

- V93000 Large (64-slot) Test Head

- V93000 Compact (16-slot) Test Head

- Memory Test Cards:

- HSM6800

- HSM4000

- HSM3G

- High-Speed Extension Card: HSM HX

- Device Power Supplies: DC Scale DPS32 and MS-DPS cards

- System Controller: High Performance HP-LX Workstation

- Software: HSM Memory Test Software Bundle

### **Related Information**

For more information about the V93000 HSM6800, please visit the following website: www.advantest.com.

#### **Contact Information**

For more information about the V93000 Direct-Probe Solution, please contact your local Advantest sales representative. **www.advantest.com**