## **ADVANTEST**

# **Digital Module**

128ch 800Mbps Digital Module 128ch 250Mbps Capable Digital Module

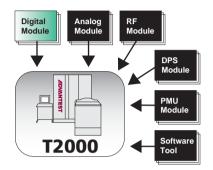

A Complete 128 Channel 250/500/800 Mbps Digital Test Module for the T2000 Test System

#### T2000 Digital Module

- Multiple-device parallel testing is achieved with 128 I/O channels per module using high-density packaging technology.

- An optimal pattern and clock frequency that meets customer's needs can be selected by the software license.

- Each channel is equipped with a driver, comparator, DC and frequency testing functionality, as well as large capacity memory to store patterns of large size to support the ever-increasing quantity of test patterns.

- In addition to functional and DC testing, the module is equipped with standard features that allows the flexibility to test various functions such as scan pattern generator, algorithmic pattern generator, high voltage pin, multi-time domain, etc.

#### 800Mbps Digital Module

- Supports source synchronous mode and measurement of DDR interface used by SoC devices, etc.

- A license can be selected from four frequencies, namely, 800M, 500M, 250M and 125Mbps.

#### 250Mbps Capable Digital Module

- One histogram counter is provided per 32 channels that allows digital output data from an AD converter to accumulate in a real-time histogram for precise and efficient analysis.

- Supports multiple small-pin device simultaneous measurement to provide simultaneous measurement of up to 8 devices of 16 channels per module.

- A license can be selected from two frequencies, namely, 250M and 125Mbps.

### **T2000** Digital Module Specifications

| Functional Test Speed         Up to 125MHz in Normal Mode         with 800Mbps/license:           Up to 250Mbps in Double Mode         Up to 400Mbps/d00MHz in Normal Mode           Up to 400Mbps/d00MHz in Double Mode         Up to 400Mbps/d00MHz in Double Mode           Up to 105Mbps/125MHz in Normal Mode         Up to 300Mbps in Quad Mode (Driver only)           Timing         0 to 125Mbps/125MHz in Normal Mode           Up to 125Mbps/125MHz in Normal Mode         Up to 500Mbps in Quad Mode (Driver only)           Timing         6 Timing Edges per Channel           Timesets: 32 Local, 1024 Global         7.8125ps period and edge resolution           Change period and edge resolution         150ps Edge Placement Accuracy           ±200ps Edge Placement Accuracy         150ps Edge Placement Accuracy           ±200ps Edge Placement Accuracy         150ps Edge Placement Accuracy           ±200ps Edge Placement Accuracy         1256K Pattern List Memory           64M x 3-bits Pattern Memory per channel         4K subroutine memory per Scan Pattern Generator, per channel           16 Channel Linkable mode (26bit x 2-bits)         16 Channel           16 Channel Linkable mode (26bit x 2-bits)         16 Channel           16 Channel Linkable mode (26bit x 2-bits)         16 Channel           16 Channel Linkable mode (26bit x 2-bits)         16 Channel           16 Channel Linkable mode (26bit x 2-bits)<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | 128ch 250Mbps Digital Module Specifications  | 128ch 800Mbps Digital Module Specifications               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------|-----------------------------------------------------------|

| Up to 250Mbps in Double Mode         Up to 200Mbps/200MHz in Normal Mode           Up to 300Mbps/200MHz in Double Mode         Up to 300Mbps in Quad Mode (Driver only)           with 500Mbps in Quad Mode (Driver only)         Up to 125Mbps/125MHz in Normal Mode           Up to 125Mbps/125MHz in Double Mode         Up to 250Mbps/250MHz in Double Mode           Up to 125Mbps/125MHz in Normal Mode         Up to 125Mbps/125MHz in Normal Mode           Up to 250Mbps /125MHz in Double Mode         Up to 500Mbps in Quad Mode (Driver only)           Timing         6 Timing Edges per Channel           Timesets: 32 Local, 1024 Global         Change triming on-the-fly capability           ±200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           #200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           #300ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           #3100ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           #3100ps Edge Placement Accuracy         152M x 3-bits Placement Accuracy           #3100ps Edge Placement Accuracy         162M x 3-bits Placemonty mode (46b           #450prothmic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Digital IO Channels           | 128 IO channels, 8 high voltage VPP channels | 128 bidirectional channels, 2 unidirectional Vpp channels |

| Up to 400Mbps/400MHz in Double Mode           Up to 800Mbps in Quad Mode (Driver only)           with 500Mbps /250MHz in Double Mode           Up to 125Mbps/125MHz in Normal Mode           Up to 500Mbps /250MHz in Double Mode           Witiple Time Domains           200ps Edge Placement Accuracy           1200ps Edge Placement Accuracy           2100ps Edge Placement Accuracy           256K Pattern List Memory enchannel           4K Subroutine Memory per channel           4K Subroutine Memory per channel           15 Channel Linkable mode (26bit x 2-bits)           16 Channel Linkable Scan Memory mode (46b           Data Fail Memory (210Aptre: 4M per channel           ALPG Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Functional Test Speed         | Up to 125MHz in Normal Mode                  | with 800Mbps license:                                     |

| Up to 800Mbps in Quad Mode (Driver only)           with 500Mbps license:           Up to 125Mbps/125MHz in Normal Mode           Up to 125Mbps/125MHz in Normal Mode           Up to 500Mbps in Quad Mode (Driver only)           Timing           6 Timing Edges per Channel           Timesets: 32 Local, 1024 Global           7.8125ps period and edge resolution           Change timing on-the-fly capability           ±200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           2 Independent time domains per module           Change period on-the-fly capability           ±200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           Pattern Generators         256K Pattern List Memory           64M x 3-bits Pattern Memory per channel         128M x 3-bits Pattern per channel           4K Subroutine Memory per channel         4K x 3-bits reloadable subroutine memory per Scan Pattern Generator, per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Chankable Scan Memory mode (4Gb           Algorithmic Pattern Generator, per channel         Algorithmic Pattern Generator, per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Chankable scan Memory mode (4Gb           Algorithmic Pattern Generator, per channel         Algorithmic Pattern Generator, per channel           16 Channel Linkable mode (2G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               | Up to 250Mbps in Double Mode                 | Up to 200Mbps/200MHz in Normal Mode                       |

| with 500Mbps license:           Up to 125Mbps/125MHz in Normal Mode           Up to 250Mbps/250MHz in Double Mode           Up to 500Mbps in Quad Mode (Driver only)           Timing           6 Timing Edges per Channel           Timesets: 32 Local, 1024 Global           7.8125ps period and edge resolution           Change timing on-the-fly capability           ±200ps Edge Placement Accuracy           150ps Edge Placement Accuracy           2 independent time domains per module           Change period on-the-fly capability           Pattern Generators           256K Pattern List Memory per channel           64M x 3-bits Pattern Memory per channel           16 Channel Linkable mode (26bit x 2-bits)           16 Channel Kemory: 16M X 3-bits per pin           Plate Fail Memory: 120X X 2-banks           Fail Capture: Memory: 250K           Central Capture Memory: 250K           Central Capture Memory: 250K           Central Capture: Memory: 120X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                                              | Up to 400Mbps/400MHz in Double Mode                       |

| Up to 125Mbps/125MHz in Normal Mode           Up to 500Mbps/250MHz in Double Mode           Up to 500Mbps/250MHz in Double Mode           Up to 500Mbps/250MHz in Double Mode           Timing           6 Timing Edges per Channel           Timesets: 32 Local, 1024 Global           7.8125ps period and edge resolution           Change timing on-the-fly capability           =200ps Edge Placement Accuracy           =150ps Edge Placement Accuracy           2 independent time domains per module           Change period on-the-fly capability           Pattern Generators           26K Pattern List Memory           64M x 3-bits Pattern Memory per channel           4K Subroutine Memory per channel           16 Channel Linkable mode (2Gbit x 2-bits)           Fail and Capture Memories           Data Fail Memory: 16M per pin           Internal Memory (all modes always available)           Digital Capture Memory: 25K           Central Capture: 4X 3 bits per pin           Pattern Result Memory: 25K           Central Capture Memory: 4X x 512           External Memory (one mode at a time only)           Digital Acquisition/Capture Memory: 32M x 2           Pattern Result Memory: 25K           Central Capture: 4X 3 bits per pin           ALPG Pattern Capture: 4X 3 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                                              | Up to 800Mbps in Quad Mode (Driver only)                  |

| Image: Second         |                               |                                              | with 500Mbps license:                                     |

| Image         Up to 500Mbps in Quad Mode (Driver only)           Timing         6 Timing Edges per Channel           Timesets: 32 Local, 1024 Global         Timesets: 32 Local, 1024 Global           7.8125ps period and edge resolution         Change timing on-the-fly capability           ±200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           Multiple Time Domains         2 independent time domains per module           Change period on-the-fly capability         64M x 3-bits Pattern Memory per channel           4K Subroutine Memory per channel         4K x 3-bits Pattern per channel           4K Subroutine Memory per channel         4K x 3-bits reloadable subroutine memory per channel           16 Channel Linkable mode (26bit x 2-bits)         16 Channel Linkable Scan Memory (46b           Algorithmic Pattern Generator, per channel         16 Channel Linkable mode (26bit x 2-bits)           Fail and Capture Memories         Data Fail Memory: 32M x 2 banks         Fail Capture: 8K per pin           Plote Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture: 8K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture: 16M x 3 bits per pin           Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                                              | Up to 125Mbps/125MHz in Normal Mode                       |

| Timing         6 Timing Edges per Channel           Timesets: 32 Local, 1024 Global           7.8125ps period and edge resolution           Change timing on-the-fly capability           ±200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           Multiple Time Domains         2 independent time domains per module           Change period on-the-fly capability         256K Pattern List Memory           Fattern Generators         256K Pattern List Memory per channel         128M x 3-bits Pattern Generator, per channel           4K Subroutine Memory per channel         4K x 3-bits reloadable subroutine memory per Scan Pattern Generator, per channel         16 Channel Linkable scan Memory mode (4Gb Algorithmic Pattern Generator, per channel           Fail and Capture Memories         Data Fail Memory: 16M x 2-bits         16 Channel Linkable Scan Memory mode (4Gb Algorithmic Pattern Generator, per channel           Fail And Capture Memories         Data Fail Memory: 32M x 2 banks         Fail Capture: 8K per pin           ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture Memory: 32M x 2           External Memory (16M x 3 bits per pin         ALPG Pattern Capture: 16M x 3 bits per pin           Pattern Result Memory: 256K         Central Capture Memory: 32M x 2           Fail Capture: 32M per pin         ALPG Memory Map: 20M <t< td=""><td></td><td>Up to 250Mbps /250MHz in Double Mode</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |                                              | Up to 250Mbps /250MHz in Double Mode                      |

| Timing         6 Timing Edges per Channel           Timesets: 32 Local, 1024 Global           7.8125ps period and edge resolution           Change timing on-the-fly capability           ±200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           Multiple Time Domains         2 independent time domains per module           Change period on-the-fly capability         256K Pattern List Memory           Fattern Generators         256K Pattern List Memory per channel         128M x 3-bits Pattern Generator, per channel           4K Subroutine Memory per channel         24X x 3-bits reloadable subroutine memory per Scan Pattern Generator, per channel         4K x 3-bits reloadable subroutine memory per Scan Pattern Generator, per channel           Fail and Capture Memories         Data Fail Memory: 16N x 2-bits         16 Channel Linkable Scan Memory mode (4Gb Algorithmic Pattern Generator, per channel           Fail Capture Memories         Data Fail Memory: 16N x 2-bits         16 Channel Linkable Scan Memory analable)           Digital Capture Memory: 32M x 2 banks         Fail Capture: 8K per pin           ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture Memory: 16M x 512           Central Capture: Memory: 16M x 512         512           Pin Electronics         -1.25V to +7V Drive and Compare Range           VPP Pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                                              | Up to 500Mbps in Quad Mode (Driver only)                  |

| Timesets: 32 Local, 1024 Global           7.8125ps period and edge resolution           Change timing on-the-fly capability           ±200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           Multiple Time Domains         2 independent time domains per module           Change period on-the-fly capability         ±200ps Edge Placement Accuracy           Pattern Generators         256K Pattern List Memory         64M x 3-bits Pattern Memory per channel           4K Subroutine Memory per channel         4K x 3-bits Pattern per channel         4K x 3-bits reloadable subroutine memory per Scan Pattern Generator, per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Linkable Scan Memory mode (4Gb Algorithmic Pattern Generator, per channel           Fail and Capture Memories         Data Fail Memory: 16M per pin         Internal Memory (all modes always available)           Digital Capture Memory: 256K         Central Capture Memory: 4K x 512         16 Channel Linkable mode (algorithmic Pattern Generator, per channel           ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 5 bits per pin         ALPG Pattern Capture: 4K x 512           Pattern Result Memory: 256K         Central Capture Memory: 32M x 2         264 x 512           VER Pins         ALPG Pattern Capture: 4K x 512         264 x 512           Pin Electronics         -1.25V to +7V Drive and Compare Range         -2V to +6V Dr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Timing                        | 6 Timing Edge                                |                                                           |

| 7.8125ps period and edge resolution         Change timing on-the-fly capability         #200ps Edge Placement Accuracy       ±150ps Edge Placement Accuracy         Multiple Time Domains       2 independent time domains per module         Change period on-the-fly capability         Pattern Generators       256K Pattern List Memory         64M x 3-bits Pattern Memory per channel       128M x 3-bits Pattern per channel         4K Subroutine Memory per channel       4k x 3-bits reloadable subroutine memory per scan Pattern Generator, per channel         16 Channel Linkable mode (2Gbit x 2-bits)       16 Channel Linkable Scan Memory mode (4db Algorithmic Pattern Generator, per channel         Fail and Capture Memories       Data Fail Memory: 16M per pin       Internal Memory (all modes always available)         Digital Capture Memory: 256K       Central Capture: 8K per pin       ALPG Pattern Capture: 4K x 3 bits per pin         ALPG Pattern Result Memory: 256K       Central Capture Memory: 32M x 2       External Memory (one mode at a time only)         Digital Capture Sto +77V Drive and Compare Range       -2V to +6V Drive and Compare Range       -2V to +6V Drive and Compare Range         Pin Electronics       -1.25V to +77V Drive and Compare Range       -2W to +6V Drive and Compare Range       -2W to +6V Drive and Compare Range         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13.5V maximum programmable V       DC Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |                                              |                                                           |

| Change timing on-the-fly capability           ±200ps Edge Placement Accuracy         ±150ps Edge Placement Accuracy           Multiple Time Domains         2 independent time domains per module           Change period on-the-fly capability         Change period on-the-fly capability           Pattern Generators         256K Pattern List Memory           64M x 3-bits Pattern Memory per channel         128M x 3-bits Pattern per channel           4K Subroutine Memory per channel         25can Pattern Generator, up to 128M x 3-bits reloadable subroutine memory per scan Pattern Generator, up to 128M x 2-bits per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Linkable Scan Memory mode (4Gb           Fail and Capture Memories         Data Fail Memory: 16M per pin         Internal Memory (all modes always available)           Digital Capture Memory: 256K         Central Capture: 4K x 3 bits per pin         Pattern Capture: 4M per channel           ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4M x 3 bits per pin         Pattern Capture: 4M x 3 bits per pin           Pattern Result Memory: 256K         Central Capture: Memory: 16M x 512         Fail Capture: 32M per pin           Pattern Result Memory: 256K         Central Capture Memory: 16M x 512         External Memory (ane mode at a time only)           Pattern Result Memory: 256K         Central Capture: 32M x 2         Fail Capture: 32M per pin           ALPG Patte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                              | -                                                         |

| ±200ps Edge Placement Accuracy       ±150ps Edge Placement Accuracy         Multiple Time Domains       2 independent time domains per module         Change period on-the-fly capability         Pattern Generators       256K Pattern List Memory         64M x 3-bits Pattern Memory per channel       128M x 3-bits Pattern per channel         4K Subroutine Memory per channel       4K x 3-bits reloadable subroutine memory per scan Pattern Generator, per channel         16 Channel Linkable mode (26bit x 2-bits)       16 Channel Linkable Scan Memory mode (46b Algorithmic Pattern Generator, per channel         Fail and Capture Memories       Data Fail Memory: 16M per pin       Internal Memory (all modes always available)         Digital Capture Memory: 256K       Central Capture: 4K x 3 bits per pin         Pattern Result Memory: 256K       Central Capture: 4K x 512         External Memory Map: 20M       Data Fail Capture: 4M per channel         ALPG Pattern Capture: 320 x 2       Fail Capture: 320 per pin         Pattern Result Memory: 256K       Central Capture: 16M x 3 bits per pin         ALPG Pattern Capture: 4M per channel       ALPG Pattern Capture: 320 x 2         Pattern Result Memory: 256K       Central Capture: 16M x 3 bits per pin         ALPG Remory Map: 20M       Central Capture: 16M x 3 bits per pin         ALPG Memory Map: 20M       Central Capture: 16M x 3 bits per pin         ALPG Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                                              | 5                                                         |

| Multiple Time Domains         2 independent time domains per module           Change period on-the-fly capability           Pattern Generators         256K Pattern List Memory           64M x 3-bits Pattern Memory per channel         128M x 3-bits Pattern per channel           4K Subroutine Memory per channel         4K x 3-bits reloadable subroutine memory per Scan Pattern Generator, per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Linkable Scan Memory mode (4Gb Algorithmic Pattern Generator, per channel           Fail and Capture Memories         Data Fail Memory: 16M per pin         Internal Memory (all modes always available)           Digital Capture Memory: 256K         Central Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture: 16M x 3 bits per pin           Pattern Result Memory: 256K         External Memory (one mode at a time only)           Digital Acquisition/Capture Memory: 32M x 2         Fail Capture: 32M per pin           ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 3 bits per pin           ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 5 12           External Memory (one mode at a time only)         Digital Acquisition/Capture Memory: 32M x 2           Pattern Result Memory: 256K         External Memory (one mode at a time only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                                              |                                                           |

| Change period on-the-fly capability           Pattern Generators         256K Pattern List Memory         128M x 3-bits Pattern per channel           4K Subroutine Memory per channel         4K x 3-bits Pattern per channel         4K x 3-bits Pattern per channel           4K Subroutine Memory per channel         4K x 3-bits Pattern generator, per channel         4K x 3-bits Pattern generator, per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Linkable Scan Memory mode (4Gb           Fail and Capture Memories         Data Fail Memory: 16M per pin         Internal Memory (all modes always available)           Digital Capture Memory: 256K         Central Capture: 8K per pin         ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 512           Pattern Result Memory: 256K         Central Capture: 32M per pin         Fail Capture: 32M per pin         Pattern Generator, 32M x 2           Pattern Result Memory: 256K         Central Capture: Memory: 32M x 2         Fail Capture: 32M per pin         Pattern Capture: 32M per pin           Pattern Result Memory: 256K         Central Capture: 16M x 3 bits per pin         ALPG Pattern Capture: 32M per pin           Pattern Result Memory: 256K         Central Capture: 32M per pin         Fail Capture: 32M per pin           Pattern Result Memory: 256K         Central Capture: 16M x 3 bits per pin         ALPG Pattern Capture: 4K x 5 12           Pin Electronics         -1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Multiple Time Domains         |                                              |                                                           |

| Pattern Generators       256K Pattern List Memory       128M x 3-bits Pattern per channel         4K x 3-bits Pattern Memory per channel       128M x 3-bits Pattern per channel         4K Subroutine Memory per channel       4K x 3-bits relaadable subroutine memory per channel         5can Pattern Generator, up to 128M x 2-bits per channel       16 Channel Linkable subroutine memory per channel         16 Channel Linkable mode (2Gbit x 2-bits)       16 Channel Linkable Scan Memory mode (4Gb Algorithmic Pattern Generator, per channel         Fail and Capture Memories       Data Fail Memory: 16M per pin       Internal Memory (all modes always available)         Digital Capture Memory: 22M x 2 banks       Fail Capture: 8K per pin         ALPG Pattern Capture: 4M per channel       ALPG Pattern Capture: 4K x 3 bits per pin         Pattern Result Memory: 256K       Central Capture Memory: 32M x 2         Pattern Result Memory: 256K       Central Capture: 16M x 3 bits per pin         ALPG Pattern Capture: 4K x 3 bits per pin       ALPG Memory and X x 512         Pattern Result Memory: 256K       Central Capture: 16M x 3 bits per pin         ALPG Memory Map: 20M       Central Capture: 16M x 512         Pattern Capture: 32M per pin       ALPG Memory Map: 20M         Central Capture Memory: 16M x 512       -1.25V to +7V Drive and Compare Range         20W Resolution       Termination, Load, Clamp, frequency counter per channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |                                              | •                                                         |

| 64M x 3-bits Pattern Memory per channel         128M x 3-bits Pattern per channel           4K Subroutine Memory per channel         4K x 3-bits reloadable subroutine memory per Scan Pattern Generator, up to 128M x 2-bits per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Linkable Scan Memory mode (4Gb           Algorithmic Pattern Generator, per channel         16 Channel Linkable Scan Memory mode (4Gb           Fail and Capture Memories         Data Fail Memory: 16M per pin         Internal Memory (all modes always available)           Digital Capture Memory: 32M x 2 banks         Fail Capture: 8K per pin           ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture Memory: 32M x 2 banks           Fail Capture: 32M per pin         Digital Acquisition/Capture Memory: 32M x 2 banks           Pattern Result Memory: 256K         Central Capture: 16M x 3 bits per pin           Dattern Capture: 32M per pin         ALPG Pattern Capture: 32M per pin           ALPG Pattern Capture: 32M per pin         ALPG Pattern Capture: 16M x 3 bits per pin           Central Capture Memory: 16M x 512         -1.25V to +7V Drive and Compare Range           2mV Resolution         -2W to +6V Drive and Compare Range           2mV Resolution         -1.25V to +6V, 32mA Maximum           VPP Pins         8 per module, 13.5V maximum VIHH         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pattern Generators            |                                              |                                                           |

| 4K Subroutine Memory per channel         4K x 3-bits reloadable subroutine memory per<br>Scan Pattern Generator, up to 128M x 2-bits per channel         Scan Pattern Generator, per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Linkable Scan Memory mode (4Gb<br>Algorithmic Pattern Generator, per channel           Fail and Capture Memories         Data Fail Memory: 16M per pin         Internal Memory (all modes always available)           Digital Capture Memory: 32M x 2 banks         Fail Capture: 8K per pin           ALPG Pattern Capture: 4M per channel         ALPG Pattern Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture Memory: 32M x 2           External Memory (one mode at a time only)         Digital Acquisition/Capture Memory: 32M x 2           Fail Capture: Memory: 60K         Central Capture: Memory: 4K x 512           External Memory (one mode at a time only)         Digital Acquisition/Capture Memory: 32M x 2           Fail Capture: 32M per pin         ALPG Pattern Capture: 32M per pin           ALPG Memory Map: 20M         Central Capture: 16M x 3 bits per pin           Internal Memory Load, Clamp, frequency counter per channel         Proversultion           VPP Pins         8 per module, 13.5V maximum VIHH         2 per module, 13V maximum programmable V           Central DC PMU one per Module         -4V to +6V, 32mA Maximum         6V, 25mA Maximum           Central DC PMU one per Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | *                                            | 128M x 2 hits Battorn per chapped                         |

| Scan Pattern Generator, up to 128M x 2-bits per channel         Scan Pattern Generator, per channel           16 Channel Linkable mode (2Gbit x 2-bits)         16 Channel Linkable Scan Memory mode (4Gb<br>Algorithmic Pattern Generator, per channel           Fail and Capture Memories         Data Fail Memory: 16M per pin         Internal Memory (all modes always available)           Digital Capture Memory: 32M x 2 banks         Fail Capture: 8K per pin         ALPG Pattern Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture Memory: 4K x 512         External Memory (one mode at a time only)           Pattern Result Memory: 256K         Central Capture: 32M per pin         ALPG Pattern Capture: 4K x 3 bits per pin           Pattern Result Memory: 256K         Central Capture Memory: 32M x 2         External Memory (one mode at a time only)           Digital Acquisition/Capture Memory: 32M x 2         Digital Acquisition/Capture Memory: 32M x 2           Fail Capture: 32M per pin         ALPG Pattern Capture: 16M x 3 bits per pin           ALPG Pattern Capture: 16M x 3 bits per pin         ALPG Memory Map: 20M           Central Capture Memory: 16M x 512         Termination, Load, Clamp, frequency counter per channel           VPP Pins         8 per module, 13.5V maximum VIHH         2 per module, 13V maximum programmable V           VPP Pins PMU         -1.25V to +6V, 32mA Maximum         6V, 25mA Maximum           Central DC PMU one per Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |                                              | · · · · · · · · · · · · · · · · · · ·                     |

| 16 Channel Linkable mode (2Gbit x 2-bits)       16 Channel Linkable Scan Memory mode (4Gb         Algorithmic Pattern G=nerator, per channel       Data Fail Memory: 16M per pin       Internal Memory (all modes always available)         Digital Capture Memories       Data Fail Memory: 16M per pin       Internal Memory (all modes always available)         Digital Capture Memory: 32M x 2 banks       Fail Capture: 8K per pin         ALPG Pattern Capture: 4M per channel       ALPG Pattern Capture: 4K x 3 bits per pin         Pattern Result Memory: 256K       Central Capture Memory: 4K x 512         External Memory (one mode at a time only)       Digital Acquisition/Capture Memory: 32M x 2         Fail Capture: 32M per pin       Fail Capture: 32M per pin         ALPG Pattern Capture: 16M x 3 bits per pin       ALPG Pattern Capture: 16M x 3 bits per pin         Mattern Capture: 16M x 512       Fail Capture: 32M per pin         Pin Electronics       -1.25V to +7V Drive and Compare Range       -2V to +6V Drive and Compare Range         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13.V maximum programmable V         DC Measurement       -       -         Per Pin PMU       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Central DC PMU one per Module       -4V to +8V, 60mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               | • •                                          |                                                           |

| Algorithmic Pattern Generator, per channel         Fail and Capture Memories       Data Fail Memory: 16M per pin       Internal Memory (all modes always available)         Digital Capture Memory: 32M x 2 banks       Fail Capture: 8K per pin         ALPG Pattern Capture: 4M per channel       ALPG Pattern Capture: 4K x 3 bits per pin         Pattern Result Memory: 256K       Central Capture Memory: 4K x 512         External Memory (one mode at a time only)       Digital Acquisition/Capture Memory: 32M x 2         Fail Capture: 32M per pin       Fail Capture: 32M per pin         ALPG Pattern Capture: 16M x 3 bits per pin       ALPG Pattern Capture: 16M x 3 bits per pin         ALPG Pattern Capture: 16M x 3 bits per pin       ALPG Pattern Capture: 16M x 512         Pin Electronics       -1.25V to +7V Drive and Compare Range       -2V to +6V Drive and Compare Range         2mV Resolution       Termination, Load, Clamp, frequency counter per channel         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         Ot Measurement       -       -         Per Pin PMU       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testir         Maximum ADC sample width:       Single ADC: 24 bits       Sequencer initiatied: source-sync margin testir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |                                              |                                                           |

| Fail and Capture Memories       Data Fail Memory: 16M per pin       Internal Memory (all modes always available)         Digital Capture Memory: 32M x 2 banks       Fail Capture: 8K per pin         ALPG Pattern Capture: 4M per channel       ALPG Pattern Capture: 4K x 3 bits per pin         Pattern Result Memory: 256K       Central Capture Memory: 4K x 512         External Memory (one mode at a time only)       Digital Acquisition/Capture Memory: 32M x 2         Fail Capture: 32M per pin       ALPG Pattern Capture: 16M x 3 bits per pin         ALPG Pattern Capture: 16M x 3 bits per pin       ALPG Pattern Capture: 16M x 3 bits per pin         ALPG Memory Map: 20M       Central Capture Memory: 16M x 512         Pin Electronics       -1.25V to +7V Drive and Compare Range       -2V to +6V Drive and Compare Range         2mV Resolution       Termination, Load, Clamp, frequency counter per channel         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         DC Measurement       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Per Pin PMU       -1.25V to +8V, 60mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testir         Maximum ADC sample width:       Single ADC: 24 bits       Sequencer initiatied: source-sync margin testir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |                                              |                                                           |

| Digital Capture Memory: 32M x 2 banksFail Capture: 8K per pinALPG Pattern Capture: 4M per channelALPG Pattern Capture: 4K x 3 bits per pinPattern Result Memory: 256KCentral Capture Memory: 4K x 512External Memory (one mode at a time only)Digital Acquisition/Capture Memory: 32M x 2Fail Capture: 32M per pinFail Capture: 32M per pinALPG Pattern Capture: 16M x 3 bits per pinALPG Pattern Capture: 16M x 3 bits per pinALPG Memory Map: 20MCentral Capture Memory: 16M x 512Pin Electronics-1.25V to +7V Drive and Compare Range-2V to +6V Drive and Compare Range-2V to +6V Drive and Compare RangeVPP Pins8 per module, 13.5V maximum VIHH2 per module, 13V maximum programmable VDC Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                                              |                                                           |

| ALPG Pattern Capture: 4M per channel       ALPG Pattern Capture: 4K x 3 bits per pin         Pattern Result Memory: 256K       Central Capture Memory: 4K x 512         External Memory (one mode at a time only)       Digital Acquisition/Capture Memory: 32M x 2         Fail Capture: 32M per pin       ALPG Pattern Capture: 16M x 3 bits per pin         ALPG Pattern Capture: 16M x 3 bits per pin       ALPG Pattern Capture: 16M x 3 bits per pin         ALPG Memory Map: 20M       Central Capture Memory: 16M x 512         Pin Electronics       -1.25V to +7V Drive and Compare Range       -2V to +6V Drive and Compare Range         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         DC Measurement       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Per Pin PMU       -1.25V to +8V, 60mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testir         Maximum ADC sample width:       Single ADC: 24 bits       Single ADC: 24 bits       Single ADC: 24 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Fail and Capture Memories     |                                              |                                                           |

| Pattern Result Memory: 256KCentral Capture Memory: 4K x 512External Memory (one mode at a time only)Digital Acquisition/Capture Memory: 32M x 2Fail Capture: 32M per pinALPG Pattern Capture: 16M x 3 bits per pinALPG Pattern Capture: 16M x 3 bits per pinALPG Memory Map: 20MPin Electronics-1.25V to +7V Drive and Compare Range-2V to +6V Drive and Compare Range-2V to +6V Drive and Compare RangeVPP Pins8 per module, 13.5V maximum VIHH2 per module, 13V maximum programmable VDC Measurement-1.25V to +6V, 32mA Maximum6V, 25mA MaximumPer Pin PMU-1.25V to +8V, 60mA Maximum8V, 60mA MaximumOther FeatureHistogram Engine: per each 32 channelsSequencer initiatied: source-sync margin testirMaximum ADC sample width:<br>Single ADC: 24 bitsSequencer initiatied: source-sync margin testir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |                                              |                                                           |

| External Memory (one mode at a time only)         Digital Acquisition/Capture Memory: 32M x 2         Fail Capture: 32M per pin         ALPG Pattern Capture: 16M x 3 bits per pin         ALPG Memory Map: 20M         Central Capture Memory: 16M x 512         -1.25V to +7V Drive and Compare Range         -2V to +6V Drive and Compare Range         -2V to +6V Drive and Compare Range         VPP Pins         8 per module, 13.5V maximum VIHH         2 per module, 13V maximum programmable V         DC Measurement         Per Pin PMU         -1.25V to +8V, 60mA Maximum         6V, 25mA Maximum         Other Feature         Histogram Engine: per each 32 channels         Sequencer initiatied: source-sync margin testir         Maximum ADC sample width:         Single ADC: 24 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                                              |                                                           |

| Image: space of the system o |                               | Pattern Result Memory: 256K                  |                                                           |

| Image: space spac                |                               |                                              |                                                           |

| ALPG Pattern Capture: 16M x 3 bits per pin         ALPG Memory Map: 20M         Central Capture Memory: 16M x 512         Pin Electronics         -1.25V to +7V Drive and Compare Range         -2V to +6V Drive and Compare Range         -2W Resolution         Termination, Load, Clamp, frequency counter per channel         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         DC Measurement       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Central DC PMU one per Module       -4V to +8V, 60mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testir         Maximum ADC sample width:       Single ADC: 24 bits       Single ADC: 24 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | <u> </u>                                     |                                                           |

| ALPG Memory Map: 20M         Central Capture Memory: 16M x 512         Pin Electronics       -1.25V to +7V Drive and Compare Range         -2V to +6V Drive and Compare Range         2mV Resolution         Termination, Load, Clamp, frequency counter per channel         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         DC Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               | <u> </u>                                     |                                                           |

| Pin Electronics       -1.25V to +7V Drive and Compare Range       -2V to +6V Drive and Compare Range         2mV Resolution       2mV Resolution         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         DC Measurement       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Per Pin PMU       -1.25V to +6V, 32mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testir         Maximum ADC sample width:       Single ADC: 24 bits       Sequencer initiatied: source-sync margin testir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               | <u> </u>                                     |                                                           |

| Pin Electronics       -1.25V to +7V Drive and Compare Range       -2V to +6V Drive and Compare Range         2mV Resolution         Termination, Load, Clamp, frequency counter per channel         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         DC Measurement       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Per Pin PMU       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Central DC PMU one per Module       -4V to +8V, 60mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testir         Maximum ADC sample width:       Single ADC: 24 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                              | ALPG Memory Map: 20M                                      |

| 2mV Resolution         Termination, Load, Clamp, frequency counter per channel         VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         DC Measurement       -         Per Pin PMU       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Central DC PMU one per Module       -4V to +8V, 60mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testin         Maximum ADC sample width:       -       Single ADC: 24 bits       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                                              | Central Capture Memory: 16M x 512                         |

| Termination, Load, Clamp, frequency counter per channel           VPP Pins         8 per module, 13.5V maximum VIHH         2 per module, 13V maximum programmable V           DC Measurement         -         -           Per Pin PMU         -1.25V to +6V, 32mA Maximum         6V, 25mA Maximum           Central DC PMU one per Module         -4V to +8V, 60mA Maximum         8V, 60mA Maximum           Other Feature         Histogram Engine: per each 32 channels         Sequencer initiatied: source-sync margin testin           Maximum ADC sample width:         -         Single ADC: 24 bits         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pin Electronics               | -1.25V to +7V Drive and Compare Range        | -2V to +6V Drive and Compare Range                        |

| VPP Pins       8 per module, 13.5V maximum VIHH       2 per module, 13V maximum programmable V         DC Measurement       -         Per Pin PMU       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Central DC PMU one per Module       -4V to +8V, 60mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testin         Maximum ADC sample width:       Single ADC: 24 bits       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |                                              |                                                           |

| DC Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               | Termination, Load, Clamp, fr                 | equency counter per channel                               |

| Per Pin PMU       -1.25V to +6V, 32mA Maximum       6V, 25mA Maximum         Central DC PMU one per Module       -4V to +8V, 60mA Maximum       8V, 60mA Maximum         Other Feature       Histogram Engine: per each 32 channels       Sequencer initiatied: source-sync margin testin         Maximum ADC sample width:       Single ADC: 24 bits       Engine: Per each 32 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VPP Pins                      | 8 per module, 13.5V maximum VIHH             | 2 per module, 13V maximum programmable VIHH               |