## Hideo Okawara's Mixed Signal Lecture Series

# DSP-Based Testing – Fundamentals 46 Per-pin Signal Generator

Advantest Corporation, Tokyo Japan August 2012

### **Preface to the Series**

ADC and DAC are the most typical mixed signal devices. In mixed signal testing, analog stimulus signal is generated by an arbitrary waveform generator (AWG) which employs a D/A converter inside, and analog signal is measured by a digitizer or a sampler which employs an A/D converter inside. The stimulus signal is created with mathematical method, and the measured signal is processed with mathematical method, extracting various parameters. It is based on digital signal processing (DSP) so that our test methodologies are often called DSP-based testing.

Test/application engineers in the mixed signal field should have thorough knowledge about DSP-based testing. FFT (Fast Fourier Transform) is the most powerful tool here. This corner will deliver a series of fundamental knowledge of DSP-based testing, especially FFT and its related topics. It will help test/application engineers comprehend what the DSP-based testing is and assorted techniques.

#### **Editor's Note**

For other articles in this series, please visit the Advantest web site at <a href="http://www1.verigy.com/ate/news/newsletter/index.htm">http://www1.verigy.com/ate/news/newsletter/index.htm</a>

## Preface

Latest two issues talked about analog signal generation by using a digital pin driver. Actually V93000 has a solution package utilizing this technique in the system. It is named "Per Pin Signal Generator" (PPSG) which is the topic of the month. If you are interested in the tool and may want to try to use it, please consult local V93000 application engineers.

## **Overview of PPSG**

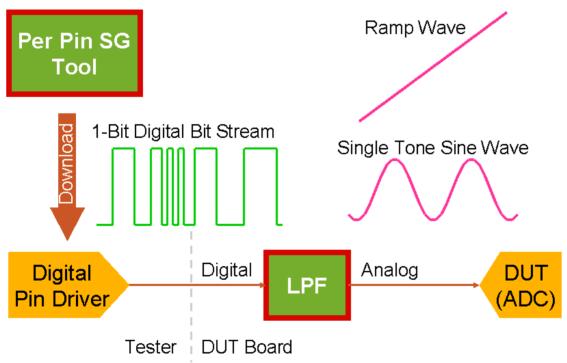

The Per Pin Signal Generator is a solution containing the tool software and the design guide of low pass filters required in the solution. The basic idea of this solution is noise shaping. The tool generates a delta-sigma bit stream containing 1's and 0's data, which is downloaded to a digital pin driver. If the output bit stream is smoothed by an appropriate low pass filter, it is turned into a sinusoid or ramp signal which the tool supports. (Figure 1) What you need is a digital pin driver and a smoothing filter on your DUT board. You don't need an AWG.

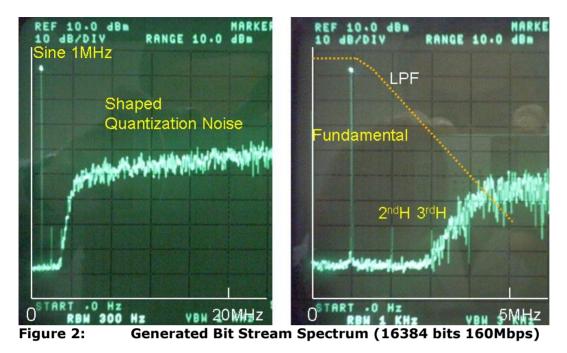

The ramp and sinusoidal waveforms are popular to test ADCs. As a matter of fact, this tool is developed to provide signals economically for ADC tests. Figure 2 shows photographs of spectrum analyzer capturing a direct NRZ digital stream signal from a digital pin driver which is programmed to generate 1MHz sinusoid. You can see the strong shaped noise in the picture. If you remove the noise with using an appropriate low pass filter, the signal becomes a beautiful sinusoid. You can notice the 2<sup>nd</sup> and 3<sup>rd</sup> harmonics still existing in the close-up picture. The noise shaping algorithm can push out the quantization noise to higher frequency range, however the harmonics of the signal has nothing to do with the noise shaping. They are generated by the asymmetry of waveform (upper half vs. lower half) generated by the digital pin driver and timing error.

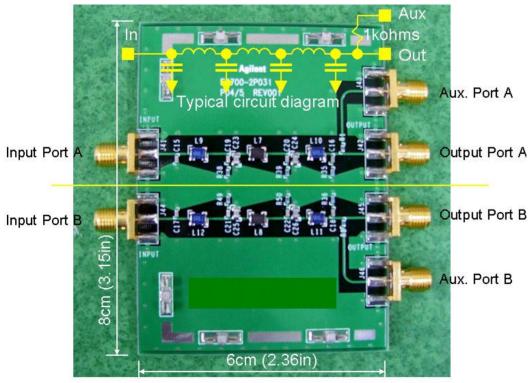

Figure 3 is a photo of a low pass filter circuits. There are two sets of low pass filters integrated in order to support a differential signal. Auxiliary ports are provided for DC calibration.

Figure 3: Low Pass Filter Photo (1.3MHz)

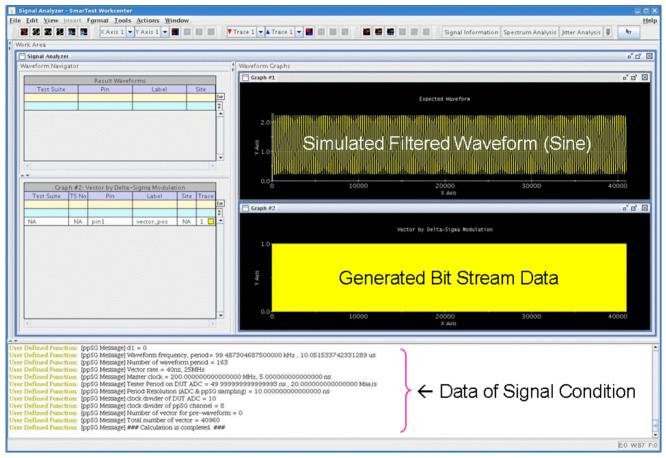

The operation of the tool is very simple, following the menus popped up one by one. Figure 4 shows an example for an ADC test. If you fill up the red marked columns, then the tool generates a waveform and code.

| 🙀 Pre Setup for Waveform Definition(Version 220                                                            | )62005a)                                 |                                     |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------|--|--|--|--|

| System Type:                                                                                               |                                          | PinScale 800, 200Mbps license 💌     |  |  |  |  |

| System Config:                                                                                             |                                          | Vigital Channel Only 💌              |  |  |  |  |

| Waveform Shape: Wavefo                                                                                     | rm: Sine or Ramp -                       | Sine                                |  |  |  |  |

| Clock domain (MCLK) of DUT ADC/DGTZ clock:                                                                 |                                          | Same domain as pin of PerPin SG 🛛 👻 |  |  |  |  |

| Which parameter should be fixed for synchronization? (Others may be adjusted): DUT ADC/DGTZ Sampling Clock |                                          |                                     |  |  |  |  |

| OK                                                                                                         |                                          |                                     |  |  |  |  |

| Sine Waveform Definition for Delta-Sigma Mod                                                               | ulation(Version 22062005a) 🔲 🗙           | Test Signal:                        |  |  |  |  |

| Frequency [Hz]:                                                                                            | 100k                                     | Frequency                           |  |  |  |  |

| Amplitude (Vpp/2) [V]:                                                                                     | 1.0                                      | Amplitude Voltage                   |  |  |  |  |

| Offset [V]:                                                                                                | 1.23                                     | Offset Voltage                      |  |  |  |  |

| Phase [Deg]:                                                                                               | 0.0                                      | 0                                   |  |  |  |  |

| DUT Input Impedance [Ohm]:                                                                                 | 1.0 M                                    |                                     |  |  |  |  |

| Signal Type:                                                                                               | Single-Ended 💌                           |                                     |  |  |  |  |

| Filter on DUT board:                                                                                       | 130k 👻                                   | Low Pass Filter Options             |  |  |  |  |

| Standard Mode(NRZ) / High Quality Mode(RZ):                                                                | Standard 🗾 👻                             |                                     |  |  |  |  |

| Pre-waveform generation time [second]:                                                                     | 0.0 m                                    |                                     |  |  |  |  |

| Waveform frequency rounding rule:                                                                          | Nearest 💌                                | ADC:                                |  |  |  |  |

| DUT ADC/DGTZ sampling frequency [Hz]:                                                                      | 20M                                      | Sampling Rate                       |  |  |  |  |

| Number of samples in Unit Test Period (integer):                                                           | 32768                                    | Number of Samples                   |  |  |  |  |

| Number of ATE clocks per DUT ADC/DGTZ sampling (integer):                                                  |                                          |                                     |  |  |  |  |

| ОК                                                                                                         |                                          |                                     |  |  |  |  |

| Ϋ Setup for .avc file 📃 🗙                                                                                  |                                          | -                                   |  |  |  |  |

| Sequencer Instruction:                                                                                     | Sequence: HALT                           | (RPTI/RPTN                          |  |  |  |  |

| repeat times for only RPTN: 1                                                                              | Number of Repeats (RPTN only)            |                                     |  |  |  |  |

| Pin name: pin1                                                                                             | PPSG Assigned Pin Name                   |                                     |  |  |  |  |

| Device Cycle Name:                                                                                         | (This is required for ".avc" file only.) |                                     |  |  |  |  |

| ОК                                                                                                         |                                          |                                     |  |  |  |  |

| Figure 4: Pull-down Menus                                                                                  | 5                                        |                                     |  |  |  |  |

The signal amplitude should actually be tuned up during online debug or inside the test flow with adjusting the "vih" and "vil" voltages of the pin driver examining the code output from the DUT ADC.

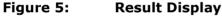

Figure 5 is the output waveform and code. The precise test conditions such as the vector period of the pin are displayed as well. You can somehow look and feel the sinusoidal striped pattern in the close-up view of the bit stream in Figure 6. The output code must be downloaded to the digital pin in the vector editor. In order to simplify the process, the bit stream pattern is generated as an ASCII file (Figure 7) which is ready for the ASCII converter to read and generate a binary vector file.

| FOF       | MAT | pi | in1; |        |

|-----------|-----|----|------|--------|

| R1        | std | Θ  | ppSG | Start; |

| R1        | std | 1  | ;    |        |

| R1        | std | Θ  | ;    |        |

| R1        | std | 1  | ;    |        |

| R1        | std | Θ  | ;    |        |

| R1        | std | 1  | 3    |        |

|           | std | Θ  | ;    |        |

| R1        | std | 1  | ;    |        |

| <b>R1</b> | std | 1  | ;    |        |

| R1        | std | Θ  | ;    |        |

| R1        | std |    | ;    |        |

| R1        | std |    | ;    |        |

| R1        | std | 1  | ;    |        |

| R1        | std | Θ  | ÷    |        |

|           | std |    | ;    |        |

|           | std |    | ;    |        |

|           | std |    | ;    |        |

| R1        | std | 0  |      |        |

| 18231     | std | 1  | ;    |        |

| R1        | std |    | ;    |        |

|           | std |    | ;    |        |

|           | std |    | 3    |        |

|           | std |    | ;    |        |

| R1        | std |    | ;    |        |

| R1        | std | 0  | ;    |        |

| R1        | std | 1  | 5    |        |

|           | std |    | ;    |        |

|           | std |    | ;    |        |

| 126.77    | std |    | ;    |        |

| R1        | std |    | ;    |        |

| R1        | std | Θ  | ;    |        |

| R1        | std | 1  | ;    |        |

|           | std | 1  | ;    |        |

| R1        | std | Θ  | ÷    | _      |

| Fig       | gur | e  | 7:   | R      |

# Figure 7: Result Bit Stream (".avc" file format)

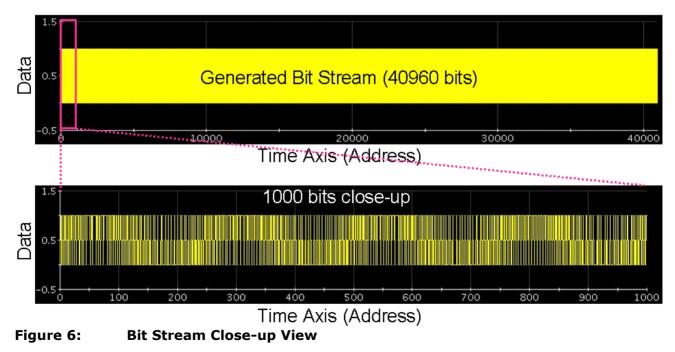

Figure 8 illustrates the experimental setup of a 10-bit ADC off the shelf tested by applying the code that the tool generates. A bit stream containing a 101kHz sinusoidal waveform is used in the linearity test based on the sine histogram method.

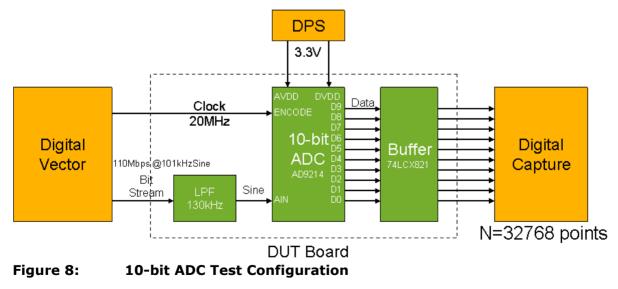

Figure 9 shows the captured code which is already shuffled in to a single sinusoid and its histogram

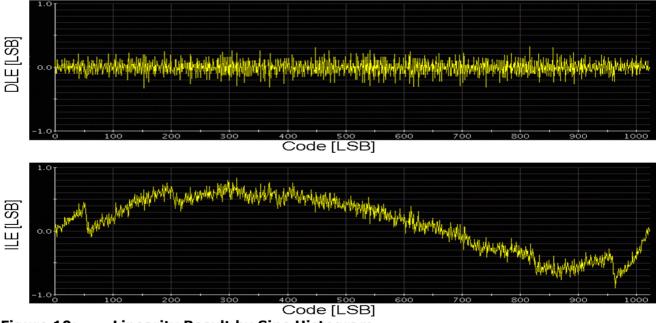

distribution. The input signal amplitude is intentionally overloaded against the input range of the ADC.<sup>1</sup> The histogram is processed appropriately and the differential linearity error (DLE) and the integral linearity error (ILE) are derived as Figure 10.

Figure 9: Sine Histogram Test at 101kHz

Figure 10: Linearity Result by Sine Histogram

<sup>&</sup>lt;sup>1</sup> DSP-based Testing Fundamentals 18 "Histogram Method in ADC Linearity Test" DSP-based Testing Fundamentals 19 "ADC Histogram Linearity – Program Examples"

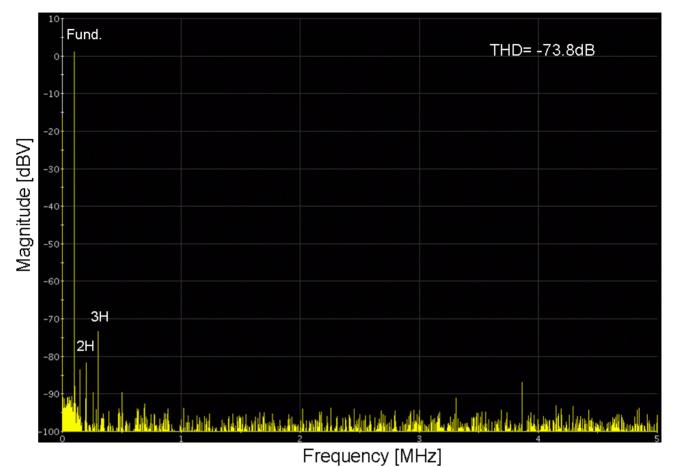

Figure 11 illustrates the FFT spectrum of the 101kHz sinusoid used in the ADC testing. A PS800 digital pin generates it with using the per-pin SG method, and multi-band AV8 (MBAV8) validates its performance.

### Figure 11: FFT Spectrum

This spectrum looks very good. The analog performance achieved by the per-pin SG method depends on the condition of the pin driver, the filter and peripheral environment. When applying this method to real application, you should carefully tune up and debug your program and conditions.