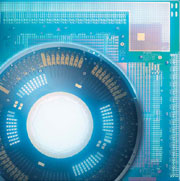

H5620 / H5620ES

H5620 / H5620ES

Memory Environmental Test System

As Server and Mobile applications have mainly led the Memory and market has also entered a super cycle that has completely withdrawn from the previous silicon cycle.

Memory capacitance will continue to rise as application of Data processing and mobile communication. However revenue will not grow as ASP goes down. Suppliers need to reduce test costs and increase profits.

H5620 contributes to reduction of test cost by integrating the test process of DRAM Burn in and Core Test. This hybrid memory test solution solves the challenge of reducing test costs while increasing test efficiency in the expanding DRAM market.

High Throughput

- High parallel test capacity (16,896device) compeered with T558x (512device)

Improvement of production environment

- Reduce accessories, equipment of Core Tester

- Reduce production space

- Reduce loss time between BI to Core test

- Supported to Full Automation (Unmanned production)

Inherit Tester OS (FutureSuite)

- Reduce TAT of test program development to translate Core Test program (Supported ATL)

- Contributing to device evaluation as using versatile tools

Global SE and FS teams locates in WW

- Deploying knowledgeable global support base in order to keep making solutions high quality & Reliable

e.g. : Program coding, debugging, correlation, maintenance